# Sustainable Semiconductor Additive Manufacturing of Micro and Nanoelectronics

Ahmed Busnaina, William Lincoln Smith Professor, Distinguished University Professor and Director of the NSF Nanoscale Science and Engineering Center for High-rate Nanomanufacturing, Northeastern University, Boston, MA and Founder and Chief Technical Officer, Nano OPS, Inc., Burlington, MA

www.nanomanufacturing.us, www.nano-ops.us

#### Introduction

- Additive Mfg. Using Directed Assembly-based Processes

- Applications in Advanced Packaging

- Printing of metal, fan out, and resistors

- Printing of dielectrics and capacitors

- Printing passive, and active devices and logic gates

- Scalable and fully automated Fab-in-a-Box

Summary

$\succ$

#### A Semiconductor Foundry in a Box

- On demand chips in a few hours

- No etching, chemical reactions, or vacuum

- Secure (trusted) foundry (from zero to full trust).

- 100 times less cost

- 100 times faster than conventional fabrication

- 1000 times reduction in materials use

- 1000 times faster than 3D printing

- 25 nm to 1000 microns feature size demonstrated

- eliminating 100s of process steps

Patented new technology (directed assembly-based printing) to print circuits at the nano and microscale funded by NSF and DoD.

Semiconductor Foundry in a Box

# How does directed assembly-based printing work?

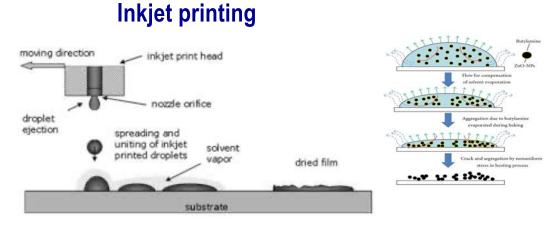

- **Directs a droplet** toward a substrate to form a pattern using many (dots) limiting pattern resolution and fidelity.

- Inherently relies on mechanical accuracy.

- Materials limited to organics and metals

#### **Directed assembly-based printing**

- Directs each nanoparticle (down to 3nm in size) toward a substrate to form a nanopattern.

- > Prints 1000 times faster & smaller patterns than inkjets

- > Prints one circuit layer per minute

### Nano @PS

# **Electrophoretic Directed Assembly– EPx Platform**

ACS Nano, 8 (5), 2014.

### Nano OPS

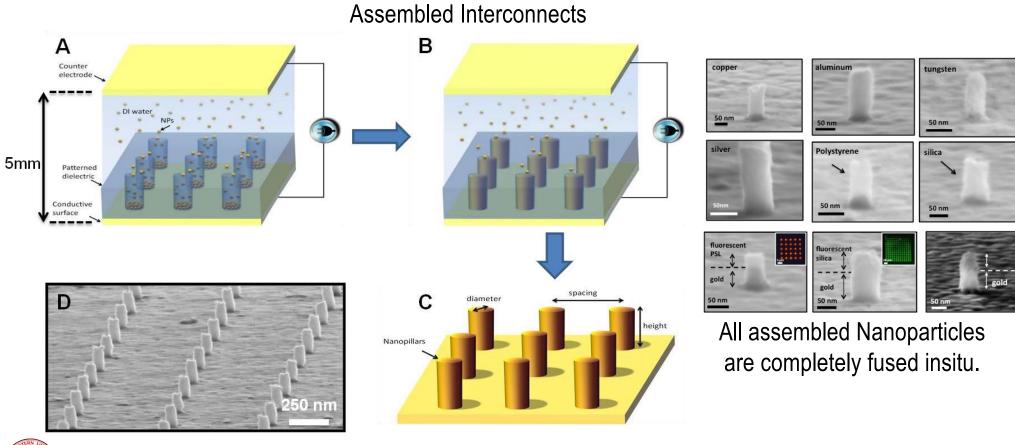

### **Interconnects Properties**

Pillar Probe

Resistance of assembled interconnects is the same as bulk (electroplated interconnects).

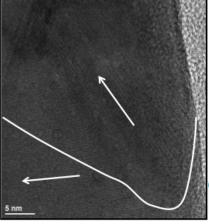

Crystalline Au Pillars

Directly assembled structures properties are equivalent to electroplating, CVD and PVD fabrication.

Directly assembled metallic structures (Cu, Ag, Al, Au, and W, etc.) in addition to semiconductors and dielectrics were demonstrated. TEM shows that NPs completely fuse without any voids at room temperature.

Nanopillars have polycrystalline nature.

ACS Nano, 8 (5), 2014.

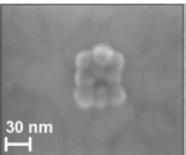

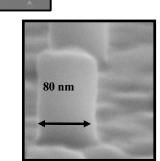

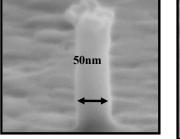

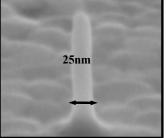

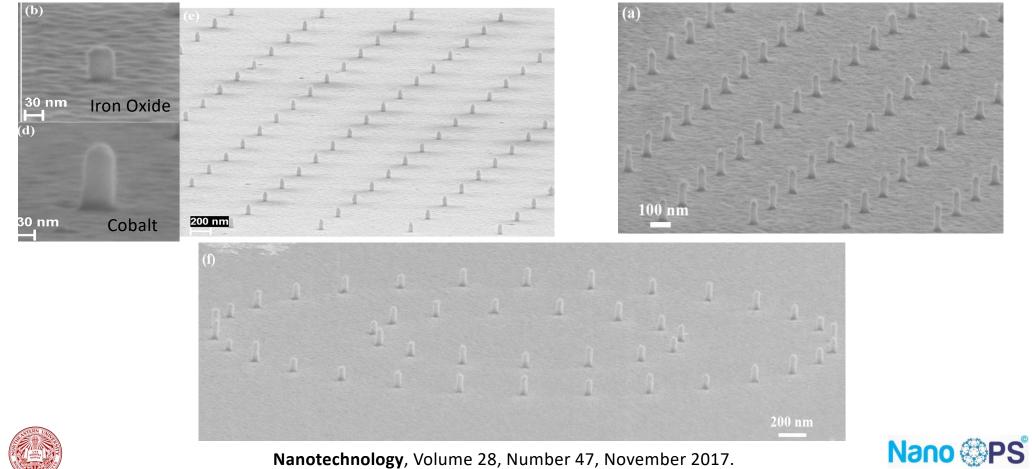

#### **Printing 3D Nanostructures**

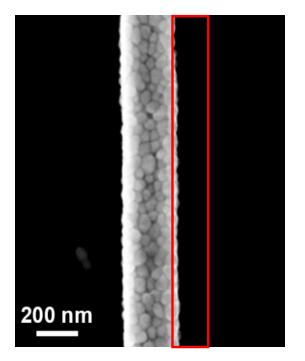

#### Images of Printed nanorods using 20 nm silica nanoparticles.

Nanotechnology, Volume 28, Number 47, November 2017.

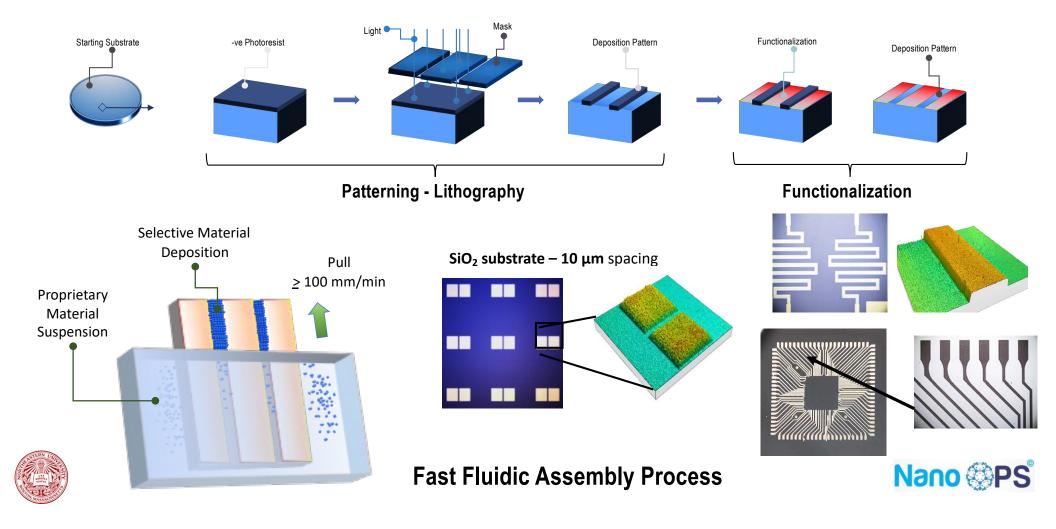

# **Fast Fluidic Assembly Process– FFx Platform**

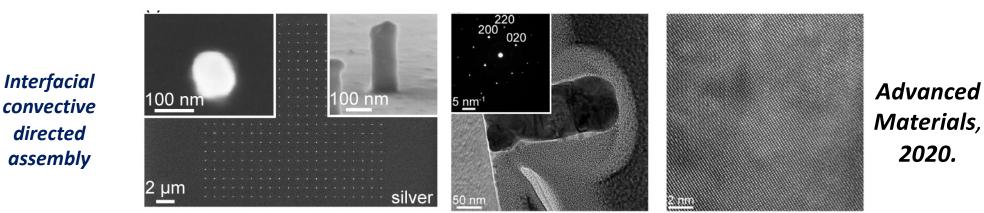

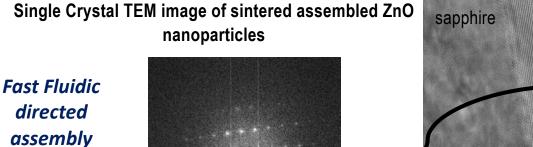

### Additively Manufacturing Single Crystal Semiconductor and Metal

Room temperature Printing & sintering to make wafer scale single crystal metal (Ag) nanostructures

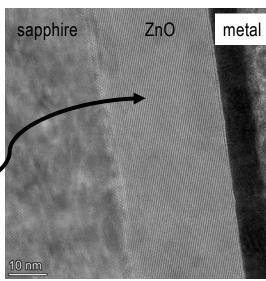

**RTP sintering of II-VI** nanoparticles (1000 c for 2 min) on sapphire yields gives a single crystal structure throughout.

### Nano <sup>OPS</sup>

5 nm<sup>-1</sup>

#### **Directed Assembly for Nanoscale Devices Review Articles**

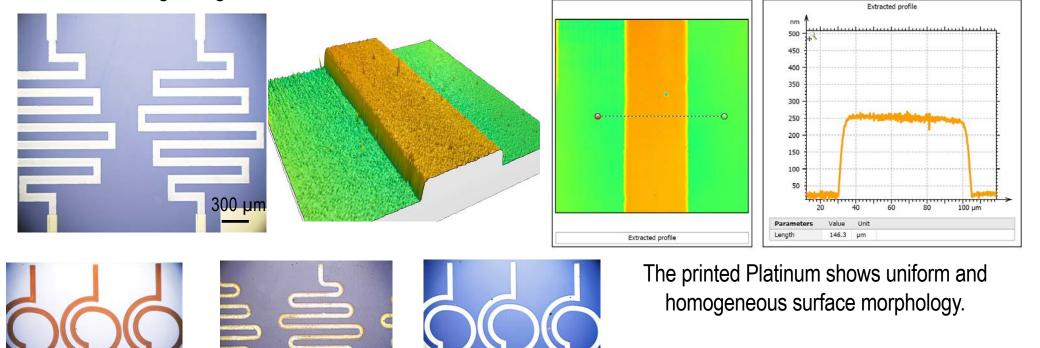

# **Profile of Metal Lines**

Confocal microscope measurements show an average platinum thickness of 250 nm after annealing using RTP at 800 °C for 2 mins .

Platinum

Gold

Copper

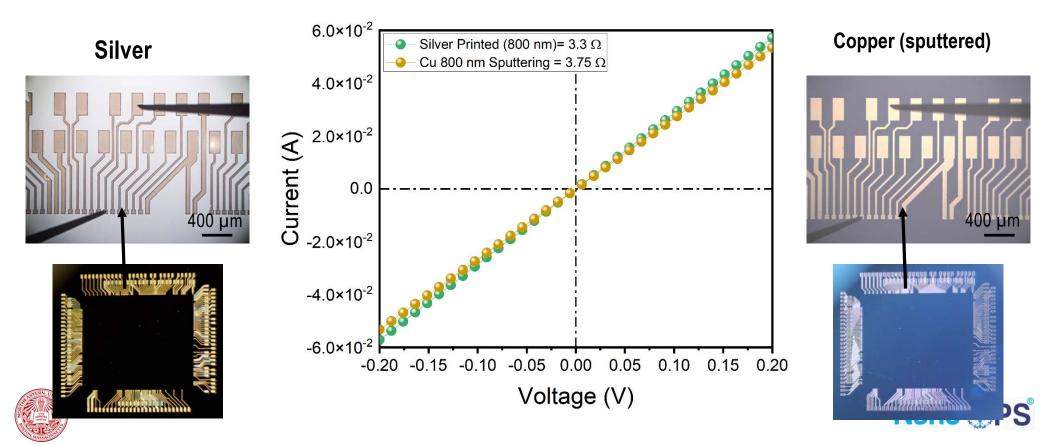

# **Additively Manufactured Silver vs Sputtered Copper**

Fan out Flip chip pattern was made using silver (internal pads < 40 microns)</li>

The trace's conductivity is equivalent to sputtered copper at the same thickness.

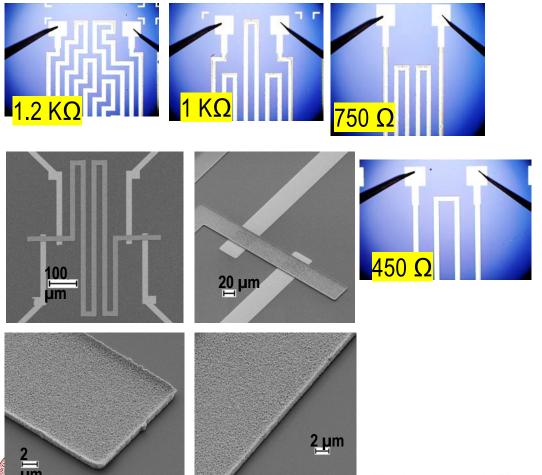

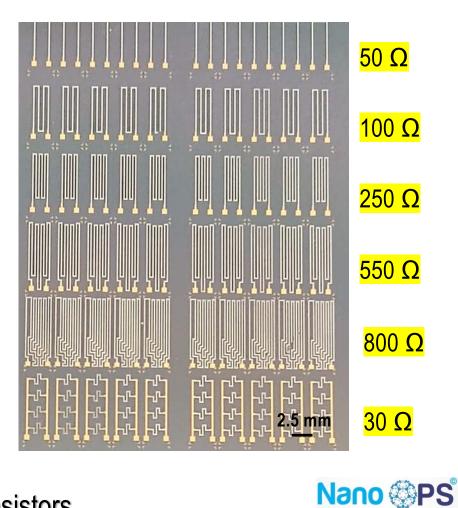

# Additively Manufactured Components: Resistors

Thin metal film resistors

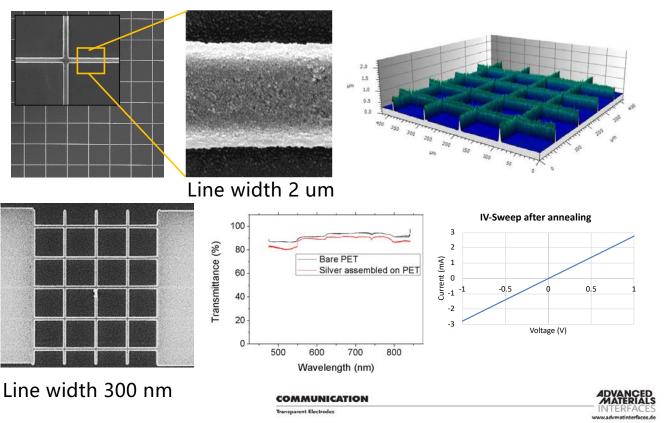

### Additively Manufactured Touch Display at the Micro and Nanoscale

Ag grids for touch display applications

Salman A. Abbasi, Zhimin Chai, and Ahmed Busnaina\*

Excellent Line edge roughness 3.7 nm Using large nanoparticles

Nano <sup>OPS</sup>

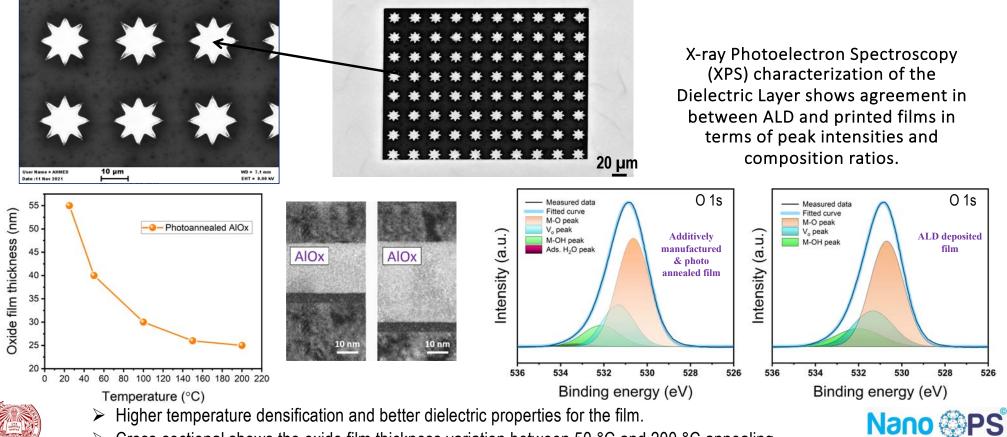

# Additively Manufactured Dielectrics

The SEM images below shows  $Al_2O_3$  micropatterns prepared by directed fluidic assembly with a dielectric constant that matches that obtained by CVD or ALD ( $\mathcal{E}_d = 7.2$ ).

Cross-sectional shows the oxide film thickness variation between 50 °C and 200 °C annealing.

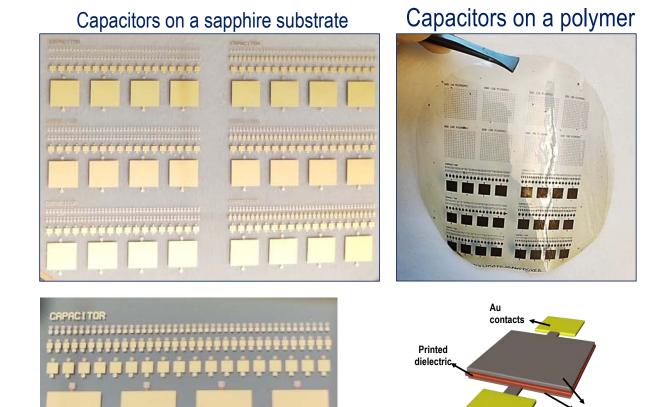

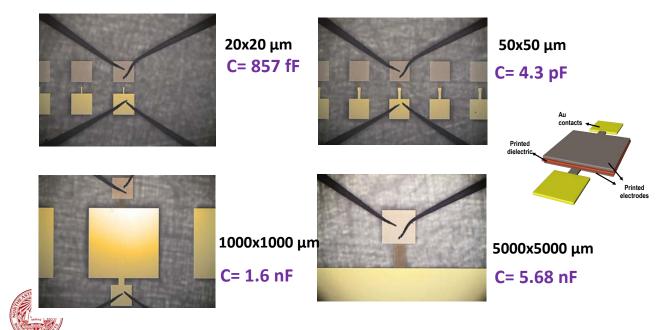

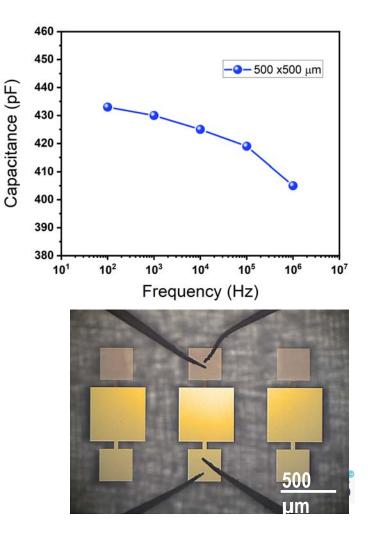

## **Additively Manufactured Capacitors on Rigid and Flexible Substrates**

- Large-scale fabricated capacitors with a dielectric layer onto sapphire or polymer substrates.

- Each substrate has 640 capacitors with different surface areas of side lengths 20, 50, 100, 500, 1000, and 5000 µm.

- ➤ Metal: Silver

- Dielectrics: Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, HfO<sub>2</sub>

Printed electrodes

Nano <sup>OPS</sup>

Capacitors on silicon

#### **Characterization of Additively Manufactured Capacitors**

- For high-frequency applications, the capacitors need to show reliable performance under high frequency.

- The curve shows the capacitance variation versus different frequencies up to 1 MHz.

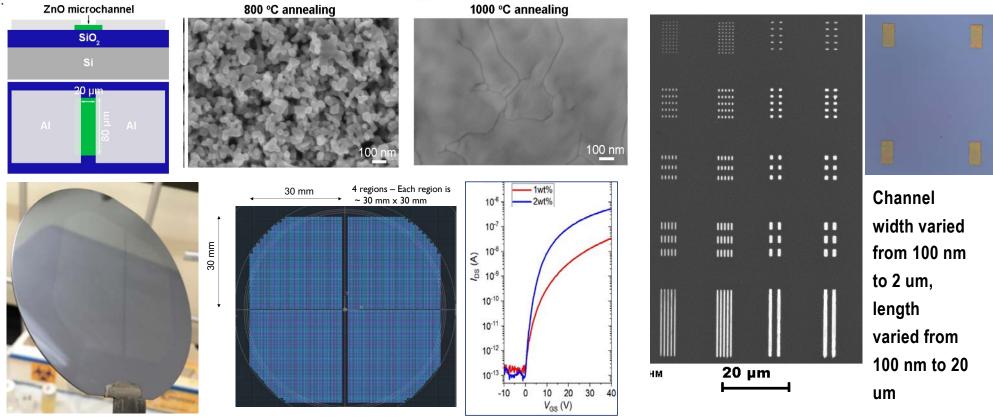

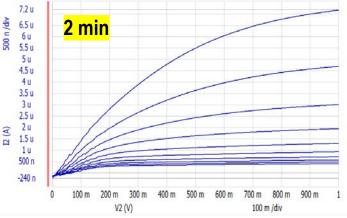

### Field Effect Transistor (FET) Using II-VI Semiconductors

Wafer-level manufacturing of 37,000 transistors exhibiting an on/off ratio higher than 10<sup>6</sup> after annealing.

ACS Applied Electronic Materials, 2023

Nano OPS

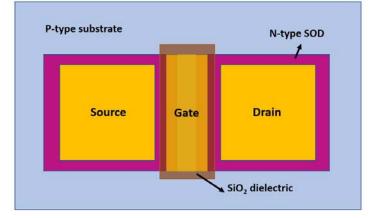

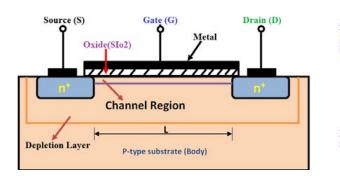

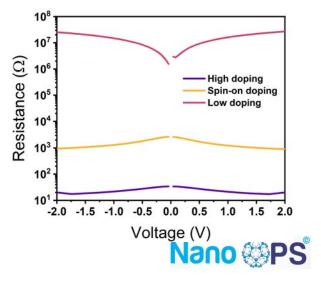

# Additively Manufactured Silicon Transistors (MOSFETs)

A fully additive liquidbased process process to manufacture MOSFETs using dopants inks.

| SOD (10 MICRONS) |

|------------------|

|                  |

|                  |

|                  |

|                  |

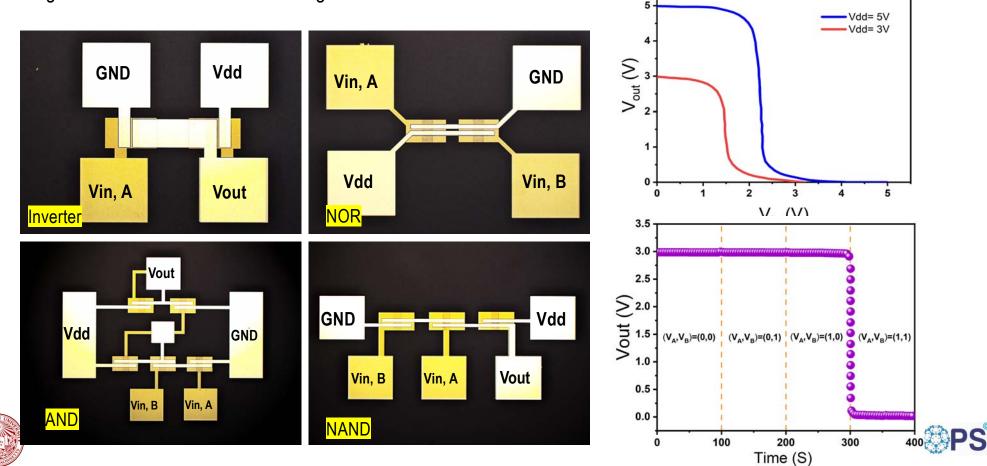

# **Additively Manufactured Logic Gate Electronics**

> Logic gates such as Inverters, AND, NAND, and NOR were printed

> The figures below show the fabricated logic circuits

### Advanced Packaging for Heterogeneous Integration for chiplet technology for integrating multiple dies in a package or system

Fully automated and cyber enabled system

- Conventional packaging approaches can not meet the resolution and density requirements.

- It can only be done at conventional fabs now.

- Submit DXF or GDS files and load ink, wafers, etc.

- > Additively Manufacture:

- micro and submicron interconnects.

- passive components

- onto silicon, glass or organic substrates (interposers)

Nano OPS

## The Future of Electronics Manufacturing

#### utomated Nanoscale Electronics Manufacturing Platform

F

https://www.youtube.com/watch?v=QpbDfAJzXDU&t=7s

### Nano <sup>OPS</sup>

# **Technological Impact**

- Adv. Packaging on demand

- Passive and Active components on demand

- Fast prototyping and development cycle

- Security

- Sustainable

MASSACHUSETTS TECHNOLOGY COLLABORATIVE

DRAPER

NEXTFLEX

Material innovation

**Raytheon**

DARPA

ROGERS